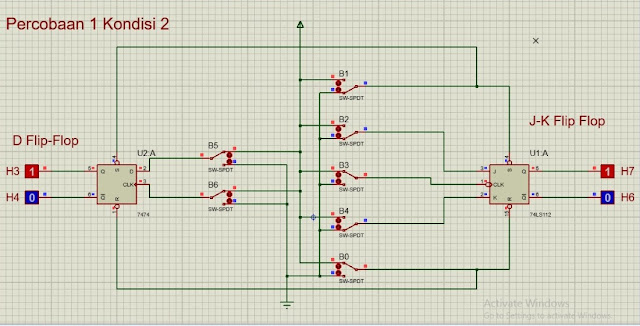

Percobaan 1 kondisi 2

Buatlah rangkaian J-K flip flop dan D flip flop seperti pada gambar pada percobaan 1 dengan ketentuan input B0=1, B1=0, B2=don’t care, B3=don’t care, B4=don’t care, B5=don’t care, B6=don’t care

2. Gambar Rangkaian Simulasi [Back]

3. Video Simulasi [Back]

4. Prinsip Kerja Rangkaian [Back]

Pada percobaan 1 kondisi 2 ini, diketahui B0=1,B1=0,B3=dontcare,B4=dont'care,B5=dont'care,dan

B6=don'tcare. Dapat dilihat pada rangkaian JK flip-flopPada rangkaian JK

flip-flop, kai high SPDT terhubung ke vcc dan kaki low SPDT terhubung ke

ground. Arus mengalir dari B1 dimana berlogika 0 mengalir ke kaki input S(Set),

sehingga input berlogikan 0. Pada B2, switch berlogika 0 dan diteruskan ke kaki

input J, pada B4 switch berlogika 0 diteruskan ke kaki K, pada CLKk diberikan

input berlogika 1, dan arus mengalir pada B0 ke kaki R(Reset). Pada gerbang

74LS112, terdapat 2 lip flop yaitu RS dan JK flip-flop. Pada JK flip-flop

diberikan input 0 0 sehingga nilai Q yaitu tetap. Dan pada input R berlogika 1 diinverterkan sehingga dalam

gerbang berlogika 0 dan pada input S diberikan input 0 sehingga dalam gerbang

berlogika 1 yang berarti input RS yaitu 0 1 yang menyebabkan nilai Q=1. Hal ini

dikarenakan nilai pada JK flip-flop tetap sehingga tidak mempengaruhi nilai RS

flip-flop.

Pada bagian D flip-flop terdapat kaki high SPDT terhubung ke vcc

dan kaki low SPDT terhubung ke ground. Pada gerbang ini terdapat 2 flip-flop

yaitu RS dan D flip-flop. Pada RS flip-flop input yang diberikan yaitu 1 0

karena ia diinverterkan sehingga pada gerbang dibaca 0 1 dengan nilai Q = 1. RS

flip-flop merupakan aktive low, dimana akan aktiv bila berlogika 0, sedangkan

pada gerbang nilai output 1 yang menyebabkan RS flip flop tidak aktif.

Sedangkan pada D flip - flop memiliki prinsip kerja jika nilai D = 0 maka nilai

Q=0. Terlihat pada gerbang diberikan input D =1 sehingga nilai output yaitu 1.

Sehingga nilai output yang terbaca pada H3 dan H4 sama dengan 1 0.

5. Link Download [Back]

Tidak ada komentar:

Posting Komentar