1. Jurnal [Back]

2. Alat dan Bahan [Back]

2.1 Alat

3. Rangkaian Simulasi [Back]

4. Prinsip Kerja Rangkaian [Back]

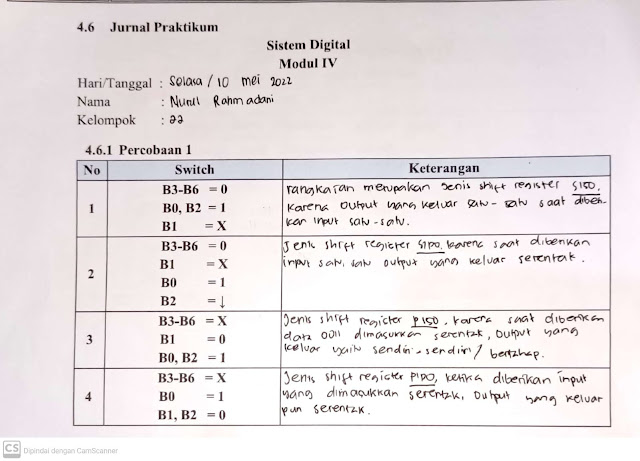

Pada percobaan 1 merupakan rangkaian Serial In/Serial Out, Paralel In/Serial Out, dan Paralel In/Paralel Out shift register dengan 4 bit. Pada rangkaian ini menggunakan D flip - flop dan merupakan jenis counter syncronous karena seluruh sumber input terhubung pada sumber CLK. Kaki high SPDT terhubung ke vcc dan kaki low SPDT terhubung ke ground. Ketika switch B3-B6 = 0, B0,B2=1, B1 = X dengan diberikan input masukan secara satu - satu maka output yang dihasilkan pun keluar satu satu, sehingga rangkaian ini disebut jenis rangkaian SISO. Dan ketika B3-B6 = X, B0 =1 , B1,B2=0 input data yang dimasukkan yaitu 1111 secara serentak , dapat dilihat pada percobaan output yang dihasilkan pun keluar serentak, sehinggal hal ini disebut sebagai jenis rangkaian PIPO (Paralel In Paralel Out).

5. Video Rangkaian [Back]

6. Analisa [Back]

1. Analisa output yang dihasilkan tiap - tiap kondisi

jawab :

Kondisi pertama

Ketika B3-B6 = 0, B0,B2=1, B1 = X, maka output yang dihaasilkan keluar 1,1 atau bergantian (bertahap), dan input data yang masuk 1,1. Sehingga kondisi ini disebut jenis shift register SISO (Serial In Serial Out)

Kondisi kedua

Pada kondisi ke-2, switch diatur B3-B6 = 0, B1 = X, B0 = 1, B2 = falltime. X pada B1 sebagai data input yang kita berikan, dan rangkaian diatur pada keadaan falltime. Input yang dimasukkan satu - satu, dan output pada rangkaian keluar serentak, sehingga disebut jenis shift register SIPO (Serial In Paralel Out).

Kondisi ketiga

Ketika B3-B6 = X, B1 = 0, B0,B2=1, dan X pada B3-B6 diberika data 0011, sehingga output yang dihasilkan keluar bertahap (satu-satu). Sedangkan input yang dimasukkan secara serentak, sehingga rangkaian ini disebut jenis rangkaian shift register PISO (Parallel In Serial Out).

Kondisi ke empat

Ketika B3-B6 = X, B0 =1 , B1,B2=0, data ynag diinputkan yaitu 1111 secara serentak. Sehingga output yang dihasilkan keluar serentak pula. Hal ini disebut jenis rangkaian shift egister PIPO (Parallel In Parallel Out).

2. Jika gerbang AND pada rangkaian dihapus, sumber clock dihubungkan langsung ke flip - flop. Bandingkan output yang didapat.

Jawab :

Ketika gerbang AND dihapuskan maka sumber clock langsung terhubung pada flip - flop dan B2 tidak terhubung, sehingga output yang ditampilkan pada probe tidak dapat diberhentikan pada salah satu angka yang diinginkan. Sedangkan ketika gerbang AND dihubungkan, B2 terhubung pada salah satu kaki AND yang menyebabkan tampilan pada probe dapat diberhentikan pada angka tertentu yang diinginkan.

.jpg)

Tidak ada komentar:

Posting Komentar