1. Jurnal [Back]

2. Alat dan Bahan [Back]

2.1 Alat

- Switch (SPDT)

3. Rangkaian Simulasi [Back]

4. Prinsip Kerja Rangkaian [Back]

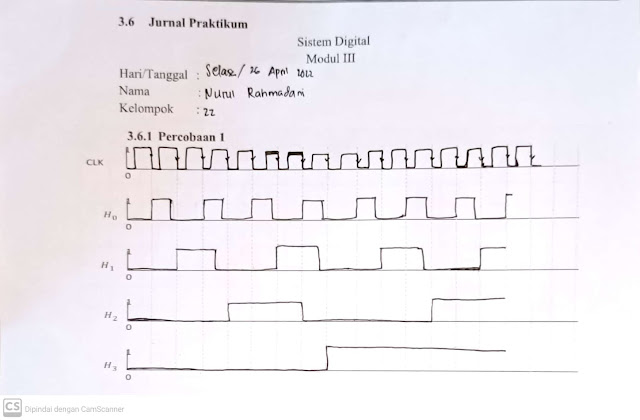

Pada percobaan 1 modul 3 ini merupakan bentuk rangkaian counter asyncronous. Hal ini diketahui karena pada clock terpasang secara seri dan hanya pada input CLK flip- flop pertama. Input untuk CLK pada flip-flop selanjutnya dipengaruhi oleh output pada flip - flop sebelumnya. Pada rangkaian ini kita menggunakan JK flip-flop atau ic 74LS112 dengan output 4 bit dan SPDT sebagai pengganti dari clock agar memudahkan saat melihat perubahan pada output. Rangkaian ini merupakan jenis rangkaian falltime, dimana ia akan aktif ketika diberikan input berlogika 0. Pada percobaan, ketika diberikan input berlogika 0 maka output pada probe H0 akan berogika 1, sedangkan pada output H1,H2, dan H3 berlogika 0 sehingga membentuk urutan biner 1000. Hal ini terjadi karena input pada flip - flop menunggu output dari flip-flop sebelumnya sehingga output yang keluar delay.

Tidak ada komentar:

Posting Komentar